1. 定时器概述

1.1 软件定时原理

使用纯软件(CPU死等)的方式实现定时(延时)功能

void delay_us(uint32_t us)

{

us *= 72;

while(us--);

}

缺点:

- 延时不精准

- CPU死等

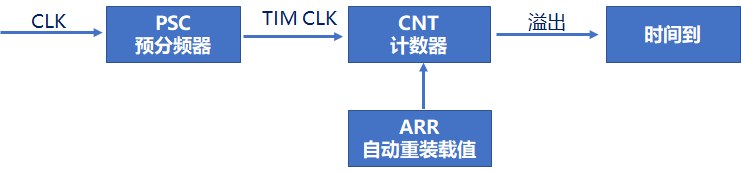

1.2 定时器定时原理

- 使用精准的时基,通过硬件的方式,实现定时功能

- 定时器核心就是计数器

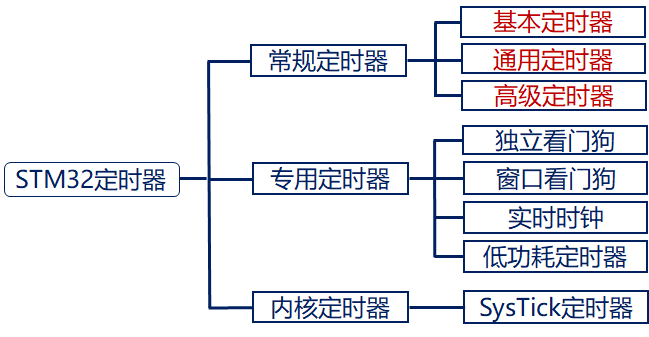

1.3 STM32定时器分类

1.4 STM32定时器特性表

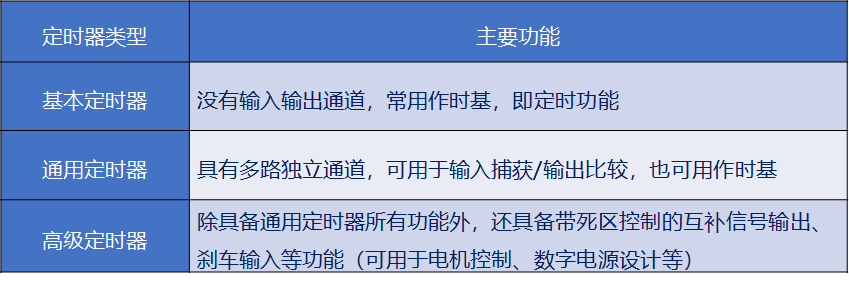

1.5 STM32基本、通用、高级定时器的功能整体区别

2. 基本定时器

2.1 基本定时器简介

- 基本定时器:TIM6/TIM7

- 主要特性:

- 16位递增计数器(计数值:0~65535)

- 16位预分频器(分频系数:1~65536)

- 可用于触发DAC

- 在更新事件(计数器溢出)时,会产生中断/DMA请求

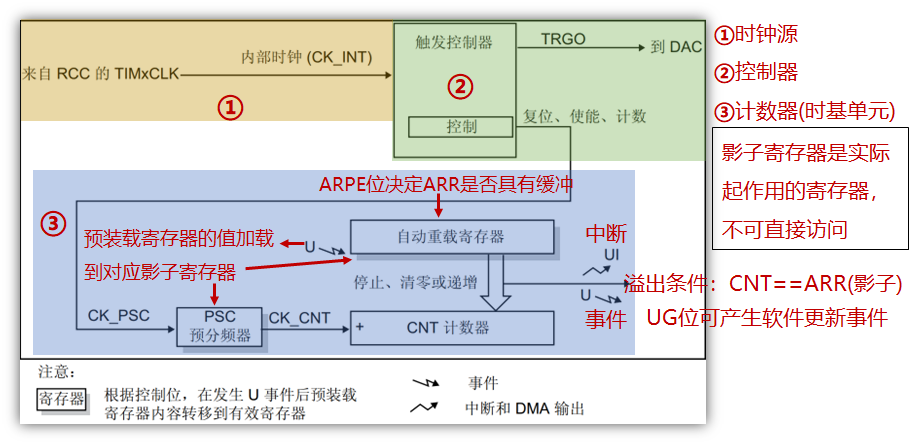

2.2 基本定时器框图

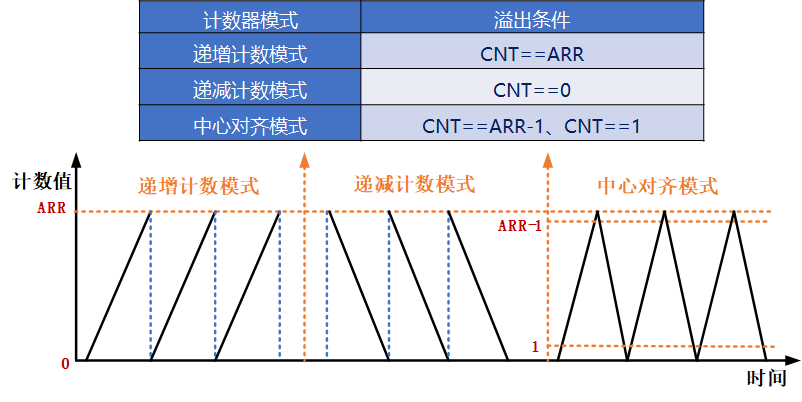

2.3 STM32定时器计数模式及溢出条件

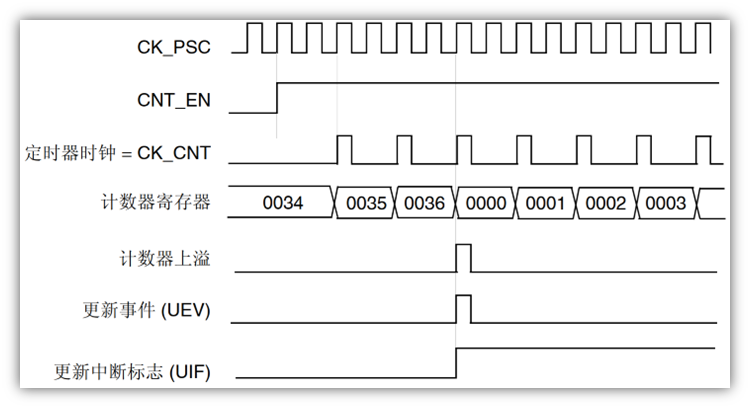

递增计数模式实例说明

- PSC = 1 (分频系数=PSC+1)

- ARR = 36

2.4 定时器中断实验相关寄存器

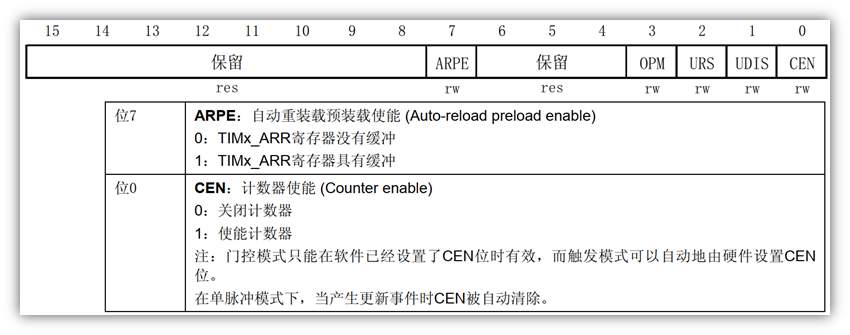

TIM6 和TIM7 控制寄存器 1(TIMx_CR1)

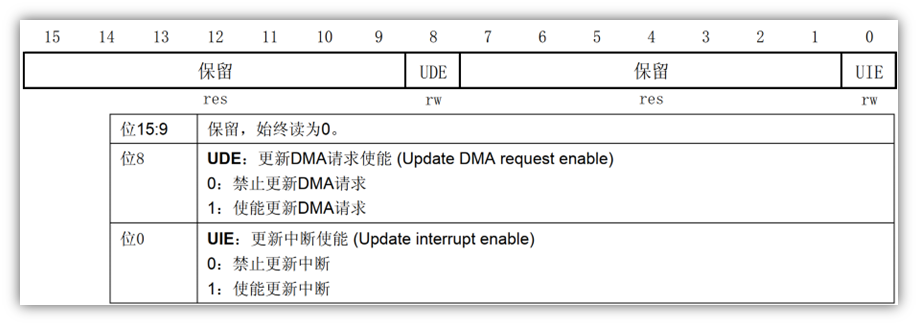

TIM6 和TIM7 DMA/中断使能寄存器(TIMx_DIER)

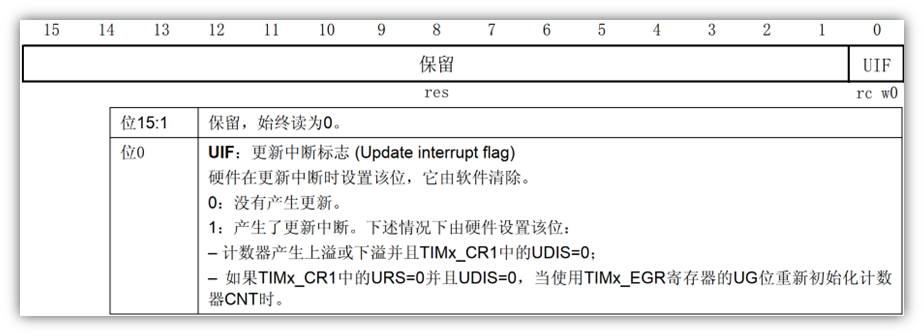

TIM6 和TIM7 状态寄存器(TIMx_SR)

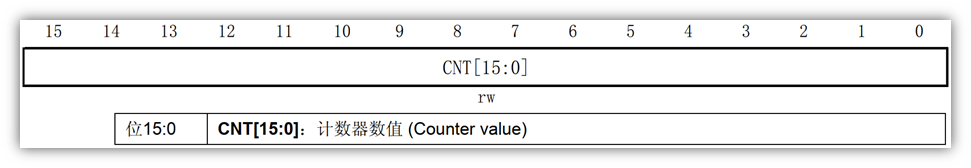

TIM6 和TIM7 计数器(TIMx_CNT)

计数器实时数值,可用于设置计时器初始值,范围:0~65535

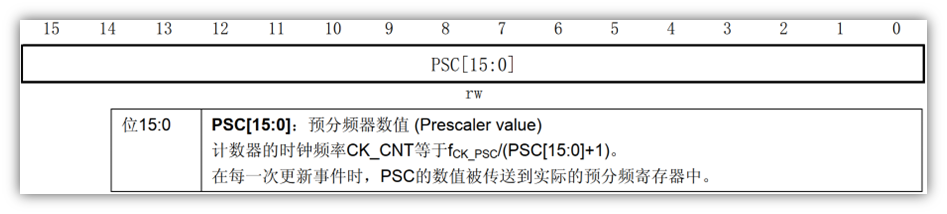

TIM6 和TIM7 预分频器(TIMx_PSC)

用于设置预分频系数,范围:0~65535,实际预分频系数等于PSC+1

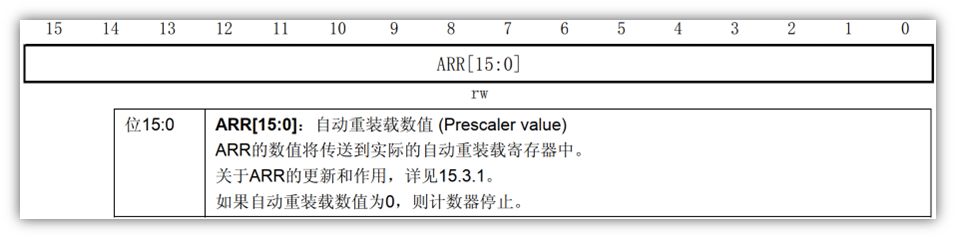

TIM6 和TIM7 自动重装载寄存器(TIMx_ARR)

用于设置自动重装载值,范围:0~65535

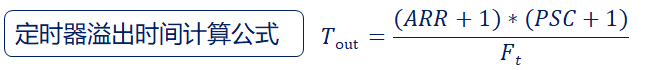

2.5 定时器溢出时间计算方法

- 𝑇out是定时器溢出时间

- 𝐹𝑡是定时器的时钟源频率

- 𝐴𝑅𝑅是自动重装载寄存器的值

- 𝑃𝑆𝐶是预分频器寄存器的值

2.6 定时器中断实验配置步骤

相关HAL库函数介绍

关键结构体介绍

typedef struct

{

TIM_TypeDef *Instance; /* 外设寄存器基地址 */

TIM_Base_InitTypeDef Init; /* 定时器初始化结构体*/

...

}TIM_HandleTypeDef;

typedef struct

{

uint32_t Prescaler; /* 预分频系数 */

uint32_t CounterMode; /* 计数模式 */

uint32_t Period; /* 自动重载值 ARR */

uint32_t ClockDivision; /* 时钟分频因子 */

uint32_t RepetitionCounter; /* 重复计数器寄存器的值 */

uint32_t AutoReloadPreload; /* 自动重载预装载使能 */

} TIM_Base_InitTypeDef;

3. 通用定时器

3.1 通用定时器简介

- 通用定时器:TIM2/TIM3 /TIM4 /TIM5

- 主要特性:

- 16位递增、递减、中心对齐计数器(计数值:0~65535)

- 16位预分频器(分频系数:1~65536)

- 可用于触发DAC、ADC

- 在更新事件、触发事件、输入捕获、输出比较时,会产生中断/DMA请求

- 4个独立通道,可用于:输入捕获、输出比较、输出PWM、单脉冲模式

- 使用外部信号控制定时器且可实现多个定时器互连的同步电路

- 支持编码器和霍尔传感器电路等

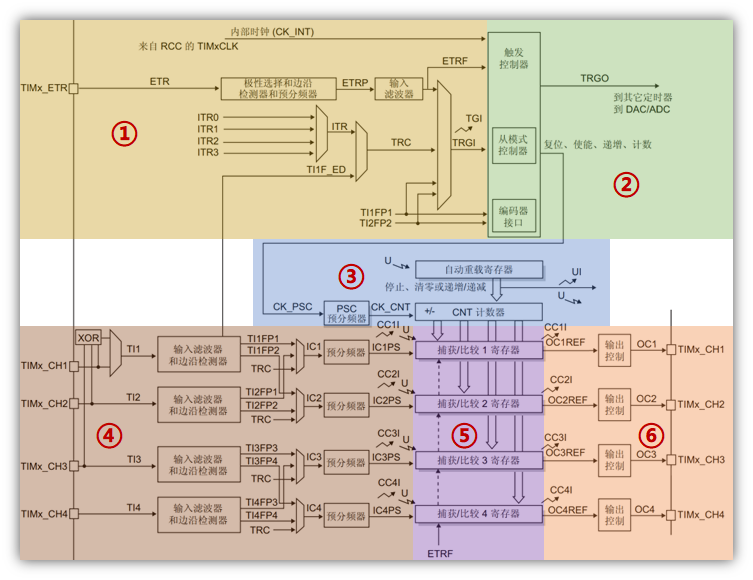

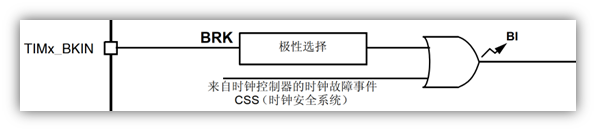

3.2 通用定时器框图

①时钟源

②控制器

③时基单元

④输入捕获

⑤捕获/比较(公共)

⑥输出比较

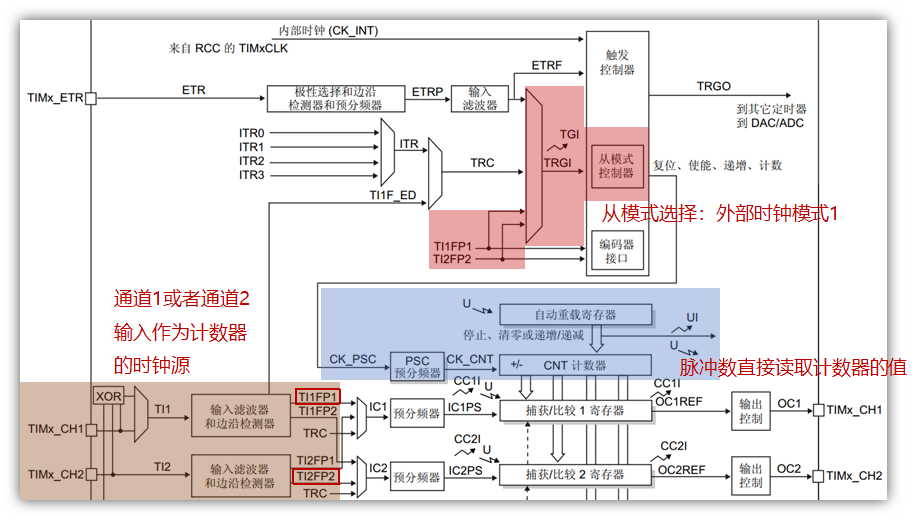

3.3 通用定时器时钟源

①内部时钟(CK_INT),来自外设总线APB提供的时钟

②外部时钟模式1:外部输入引脚(TIx),来自定时器通道1或者通道2引脚的信号

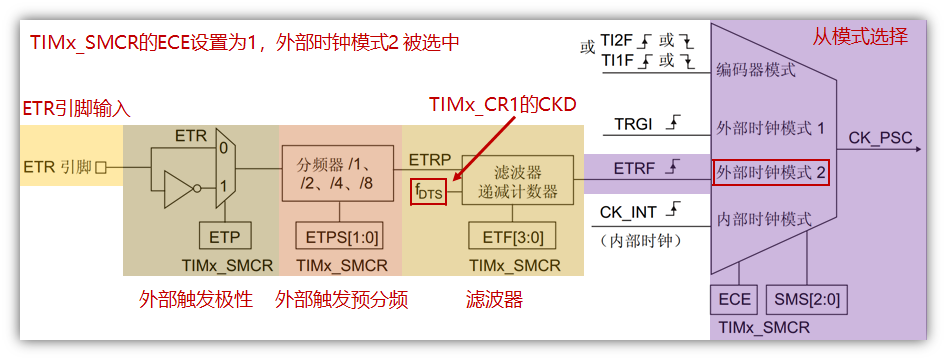

③外部时钟模式2:外部触发输入(ETR),来自可以复用为TIMx_ETR的IO引脚

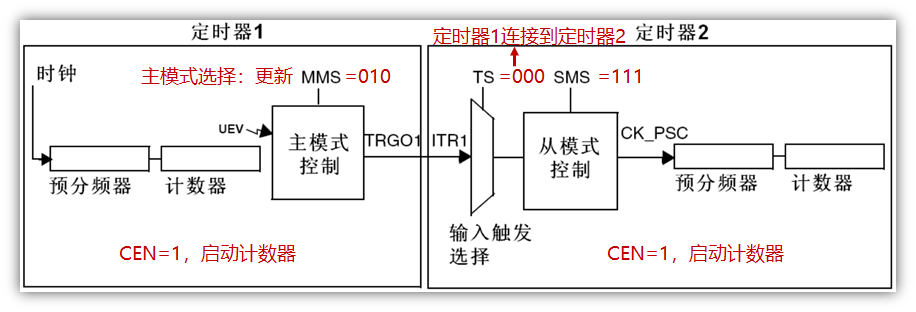

④内部触发输入(ITRx),用于与芯片内部其它通用/高级定时器级联

计数器时钟源寄存器设置方法(F1为例)

外部时钟模式1

外部时钟模式2

使用一个定时器作为另一个定时器的预分频器(F1为例)

3.4 通用定时器PWM输出

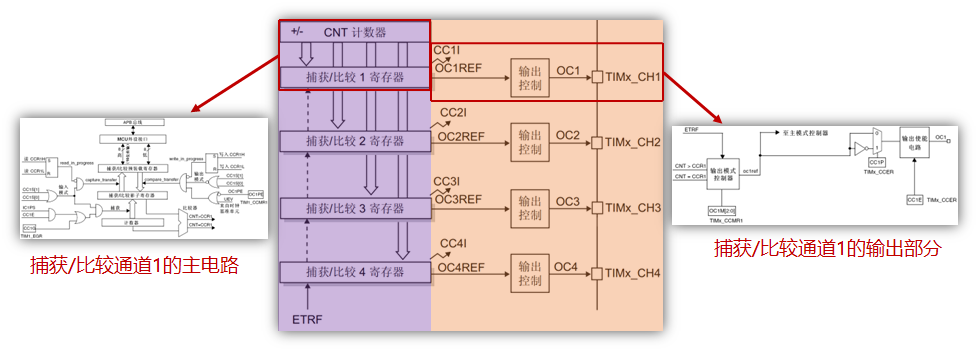

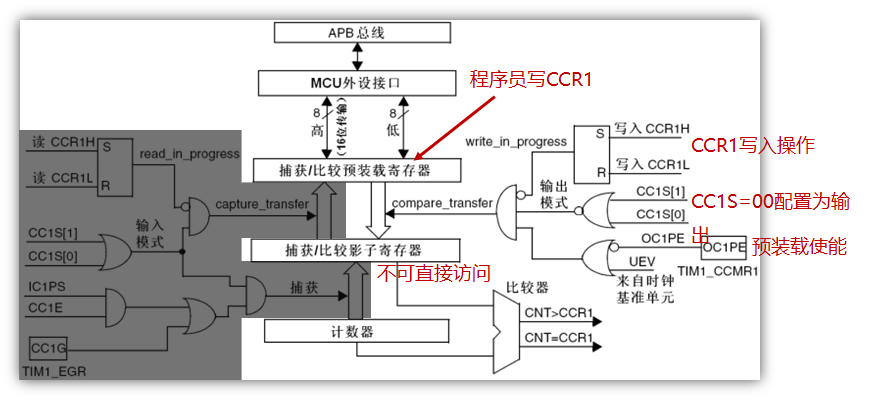

3.4.1 通用定时器输出比较部分框图介绍

捕获/比较通道1的主电路—输出部分

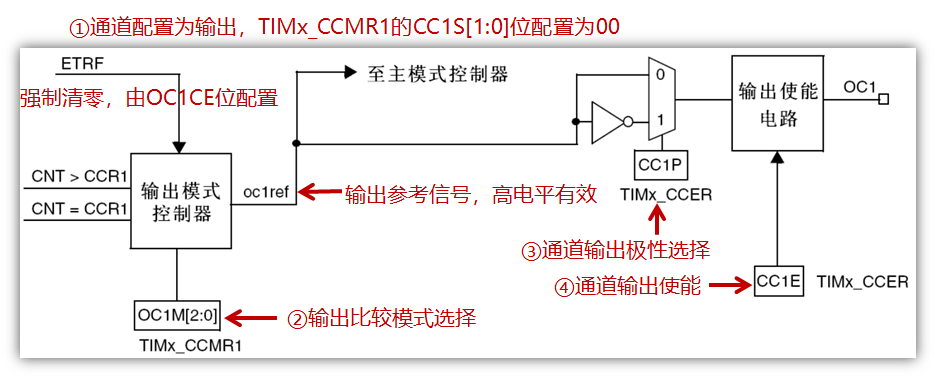

捕获/比较通道的输出部分(通道1)

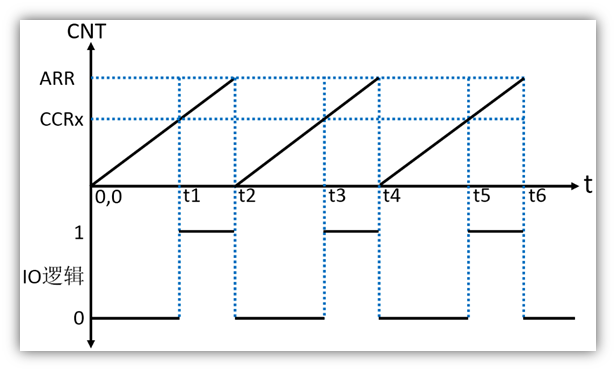

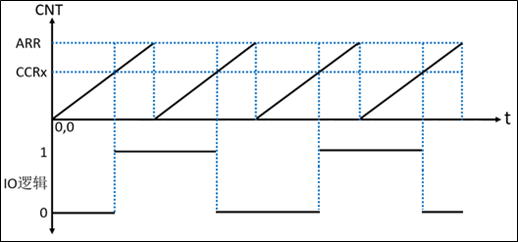

3.4.2 通用定时器输出PWM原理

- 假设:递增计数模式

- ARR:自动重装载寄存器的值

- CCRx:捕获/比较寄存器x的值

- 当CNT < CCRx,IO输出0

- 当CNT >= CCRx,IO输出1

总结:PWM波周期或频率由ARR决定,PWM波占空比由CCRx决定

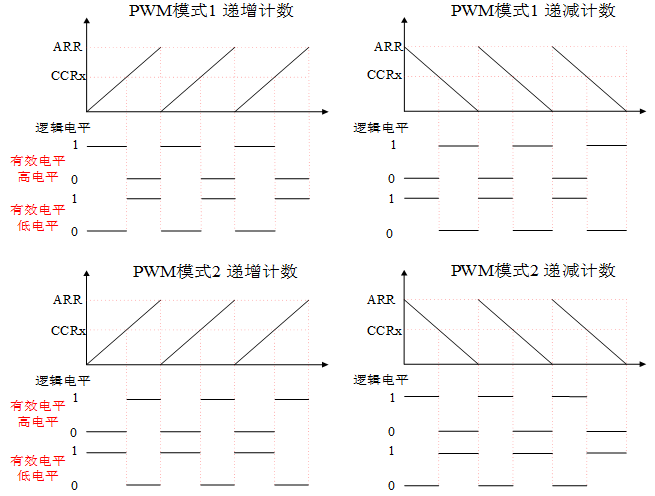

3.4.3 PWM模式

PWM模式1:

递增:

- CNT < CCRx,输出有效电平

- CNT >= CCRx,输出无效电平

递减: - CNT > CCRx,输出无效电平

- CNT <= CCRx,输出有效电平

PWM模式2:

递增:

- CNT < CCRx,输出无效电平

- CNT >= CCRx,输出有效电平

递减: - CNT > CCRx,输出有效电平

- CNT <= CCRx,输出无效电平

有/无效状态由TIMx_CCER决定

- CCxP=0:OCx高电平有效

- CCxP=1:Ocx低电平有效

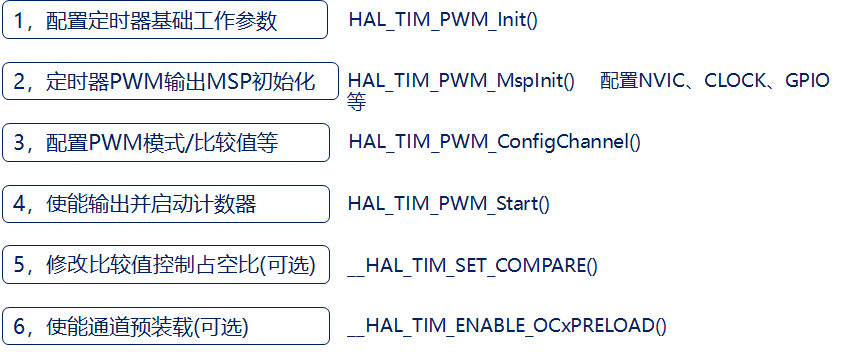

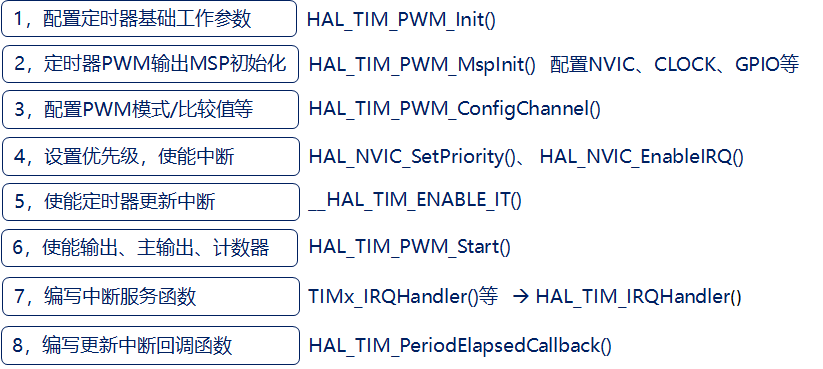

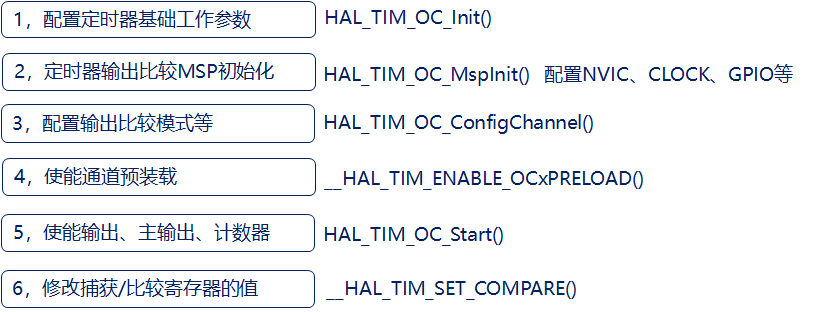

3.4.4 通用定时器PWM输出配置步骤

相关HAL库函数介绍

关键结构体介绍

typedef struct

{

uint32_t OCMode; /* 输出比较模式选择 */

uint32_t Pulse; /* 设置比较值 */

uint32_t OCPolarity; /* 设置输出比较极性 */

uint32_t OCNPolarity; /* 设置互补输出比较极性 */

uint32_t OCFastMode; /* 使能或失能输出比较快速模式 */

uint32_t OCIdleState; /* 空闲状态下OC1输出 */

uint32_t OCNIdleState; /* 空闲状态下OC1N输出 */

} TIM_OC_InitTypeDef;

3.5 通用定时器输入捕获

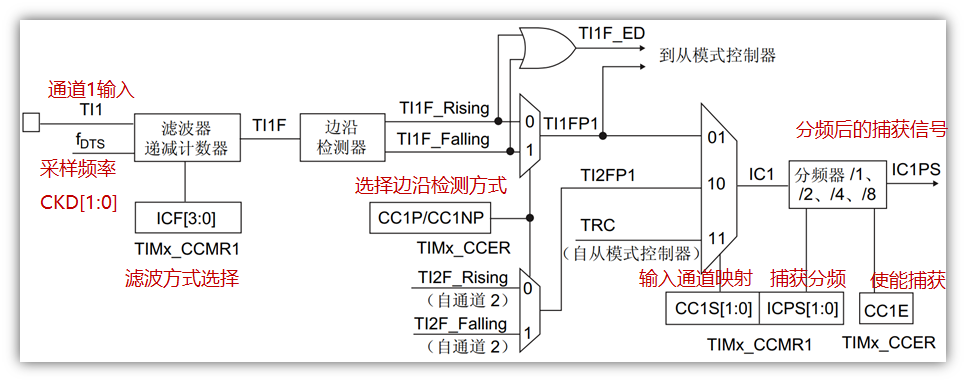

3.5.1 通用定时器输入捕获部分框图介绍

捕获/比较通道的输入部分(通道1)

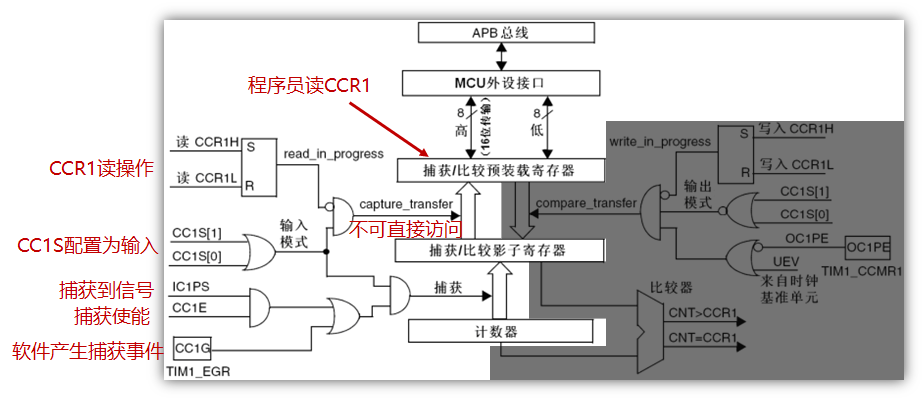

捕获/比较通道1的主电路—输入部分

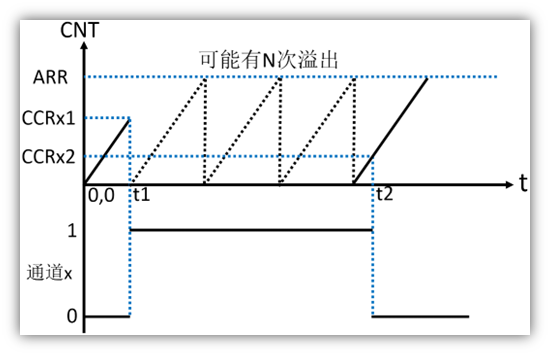

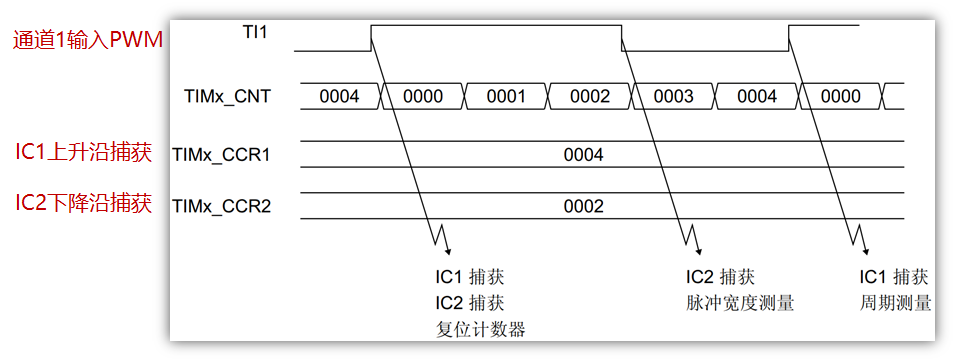

3.5.2 通用定时器输入捕获脉宽测量原理

- 以捕获测量高电平脉宽为例

- 假设:递增计数模式

- ARR:自动重装载寄存器的值

- CCRx1:t1时间点CCRx的值

- CCRx2:t2时间点CCRx的值

高电平期间,计时器计数的个数:N * (ARR+1) + CCRx2

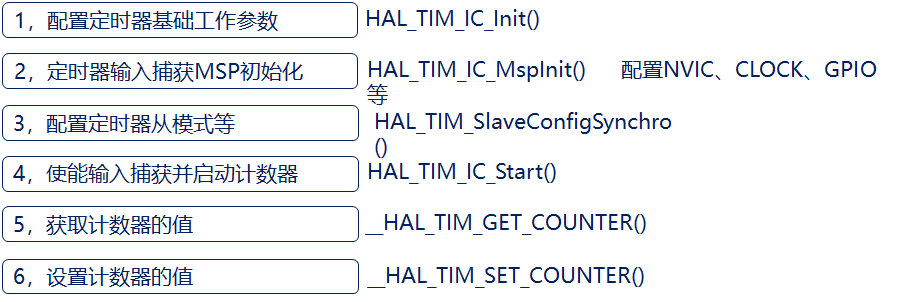

3.5.3 通用定时器输入捕获实验配置步骤

相关HAL库函数介绍

关键结构体介绍

typedef struct

{

uint32_t ICPolarity; /* 输入捕获触发方式选择,比如上升、下降沿捕获 */

uint32_t ICSelection; /* 输入捕获选择,用于设置映射关系 */

uint32_t ICPrescaler; /* 输入捕获分频系数 */

uint32_t ICFilter; /* 输入捕获滤波器设置 */

} TIM_IC_InitTypeDef;

3.6 通用定时器脉冲计数

3.6.1 脉冲计数实验原理

外部时钟模式1

3.6.2 通用定时器脉冲计数配置步骤

相关HAL库函数介绍

关键结构体介绍

typedef struct

{

uint32_t SlaveMode; /* 从模式选择 */

uint32_t InputTrigger; /* 输入触发源选择 */

uint32_t TriggerPolarity; /* 输入触发极性 */

uint32_t TriggerPrescaler; /* 输入触发预分频 */

uint32_t TriggerFilter; /* 输入滤波器设置 */

} TIM_SlaveConfigTypeDef;

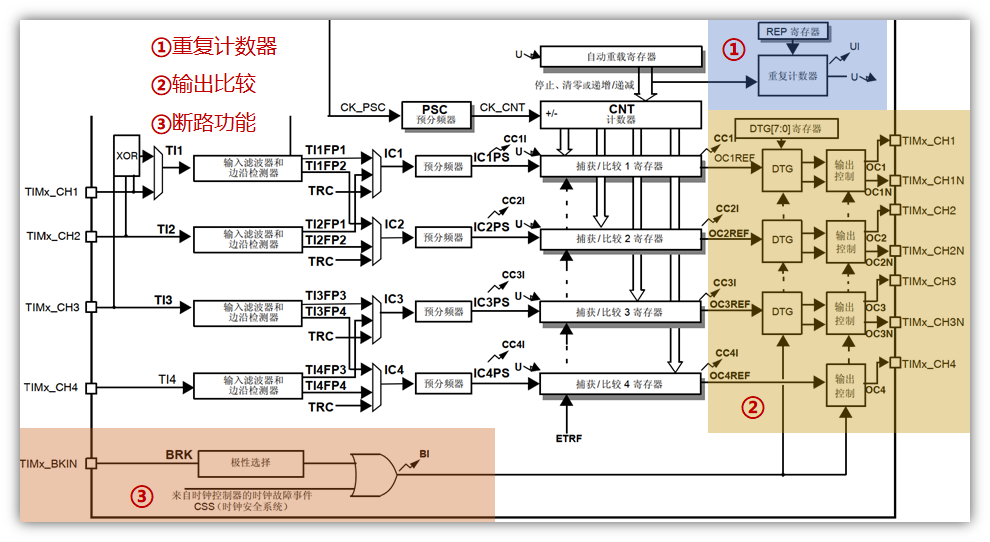

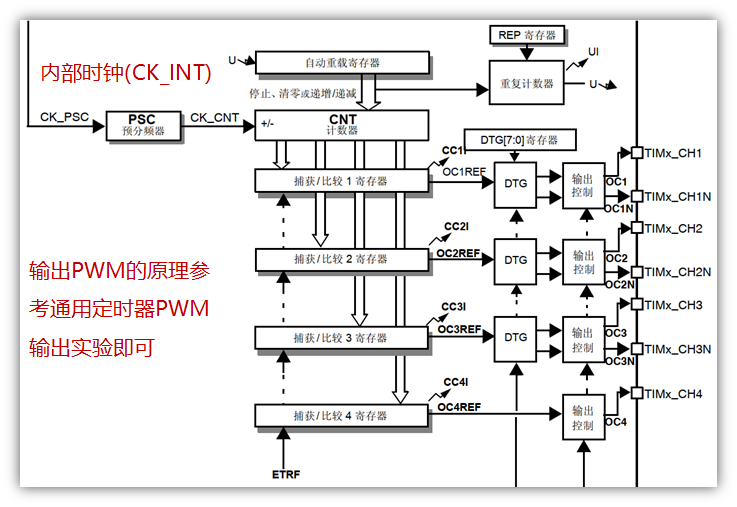

4. 高级定时器

4.1 高级定时器简介

高级定时器: TIM1/TIM8

主要特性:

- 16位递增、递减、中心对齐计数器(计数值:0~65535)

- 16位预分频器(分频系数:1~65536)

- 可用于触发DAC、ADC

- 在更新事件、触发事件、输入捕获、输出比较时,会产生中断/DMA请求

- 4个独立通道,可用于:输入捕获、输出比较、输出PWM、单脉冲模式

- 使用外部信号控制定时器且可实现多个定时器互连的同步电路

- 支持编码器和霍尔传感器电路等

- 重复计数器

- 死区时间带可编程的互补输出

- 断路输入,用于将定时器的输出信号置于用户可选的安全配置中

4.2 高级定时器框图

4.3 高级定时器输出指定个数PWM

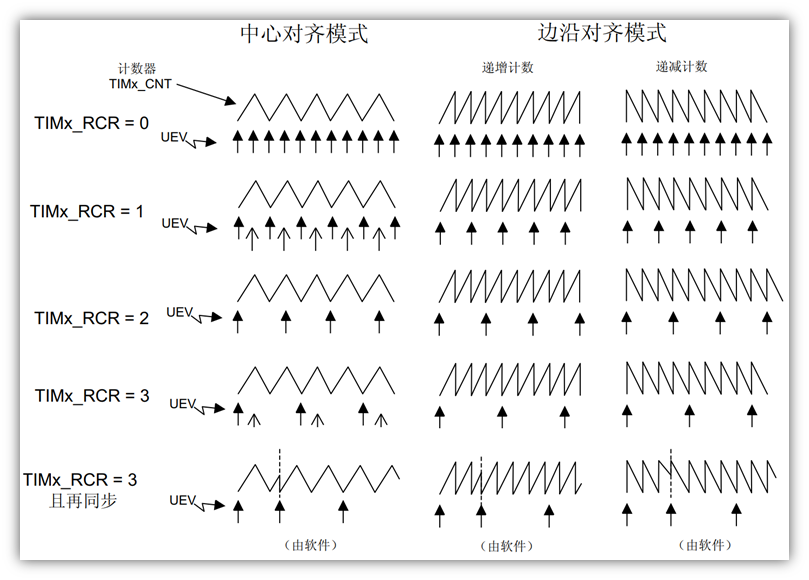

4.3.1 重复计数器特性

- 计数器每次上溢或下溢都能使重复计数器减1,减到0时,再发生一次溢出就会产生更新事件

- 如果设置RCR为N,更新事件将在N+1次溢出时发生

4.3.2 高级定时器输出指定个数PWM原理

- 配置边沿对齐模式输出PWM

- 指定输出N个PWM,则把N-1写入RCR

- 在更新中断内,关闭计数器

注意:高级定时器通道输出必须把MOE位置1

4.3.3 高级定时器输出指定个数PWM配置步骤

相关HAL库函数介绍

关键结构体介绍

typedef struct

{

uint32_t OCMode; /* 输出比较模式选择 */

uint32_t Pulse; /* 设置比较值 */

uint32_t OCPolarity; /* 设置输出比较极性 */

uint32_t OCNPolarity; /* 设置互补输出比较极性 */

uint32_t OCFastMode; /* 使能或失能输出比较快速模式 */

uint32_t OCIdleState; /* 空闲状态下OC1输出 */

uint32_t OCNIdleState; /* 空闲状态下OC1N输出 */

} TIM_OC_InitTypeDef;

4.4 高级定时器输出比较模式实验

4.4.1 高级定时器输出比较模式原理

- 输出比较模式:翻转

- 当CNT = CCRx,OCxREF电平翻转

- 总结:PWM波周期或频率由ARR决定,占空比固定50%,相位由CCRx决定

4.4.2 高级定时器输出比较模式配置步骤

相关HAL库函数介绍

关键结构体介绍

typedef struct

{

uint32_t OCMode; /* 输出比较模式选择 */

uint32_t Pulse; /* 设置比较值 */

uint32_t OCPolarity; /* 设置输出比较极性 */

uint32_t OCNPolarity; /* 设置互补输出比较极性 */

uint32_t OCFastMode; /* 使能或失能输出比较快速模式 */

uint32_t OCIdleState; /* 空闲状态下OC1输出 */

uint32_t OCNIdleState; /* 空闲状态下OC1N输出 */

} TIM_OC_InitTypeDef;

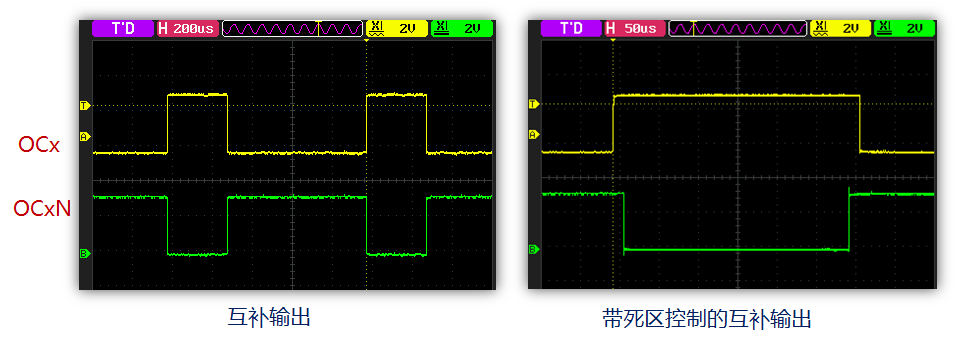

4.5 高级定时器互补输出带死区控制

4.5.1 互补输出与死区控制介绍

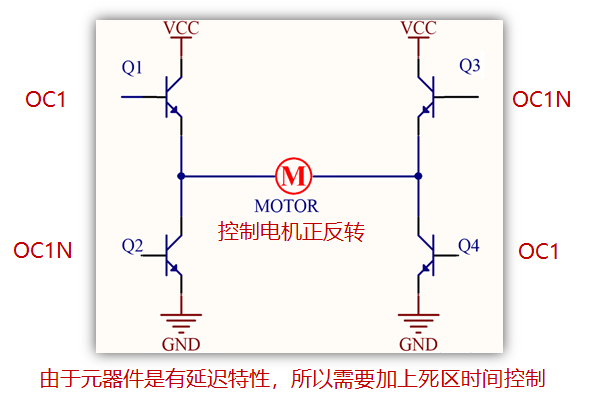

4.5.2 带死区控制的互补输出应用之H桥

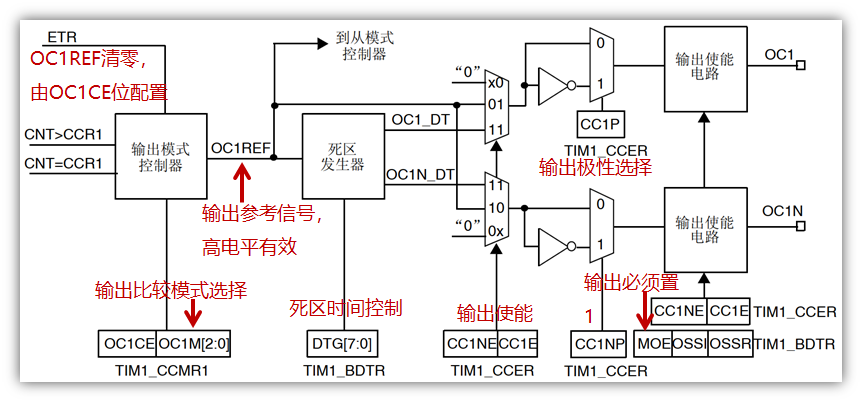

4.5.3 捕获/比较通道的输出部分(通道1至3)

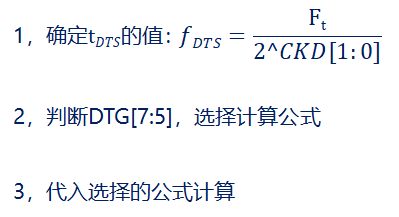

4.5.4 死区时间计算

- 举个栗子(F1为例):DTG[7:0]=250

- 250,即二进制:1111 1010,选第四条

- DT = (32+26)1655.56 ns=51.55968us

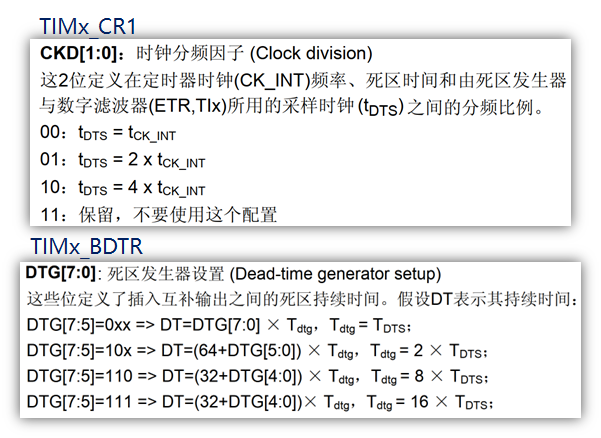

4.5.5 刹车(断路)功能

- 使能刹车功能:将TIMx_BDTR的BKE位置1,刹车输入信号极性由BKP位设置

- 使能刹车功能后:由TIMx_BDTR的MOE、OSSI、OSSR位,

- TIMx_CR2的OISx、OISxN位,TIMx_CCER的CCxE、CCxNE位控制OCx和OCxN输出状态

- 无论何时,OCx和OCxN输出都不能同时处在有效电平

发生刹车后,会怎么样

- MOE位被清零,OCx和OCxN为无效、空闲或复位状态(OSSI位选择)

- OCx和OCxN的状态:由相关控制位状态决定,当使用互补输出时:根据情况自动控制输出电平,参考参考手册使用刹车(断路)功能小节

- BIF位置1,如果使能了BIE位,还会产生刹车中断;如果使能了TDE位,会产生DMA请求

- 如果AOE位置 1,在下一个 更新事件UEV时,MOE位被自动置 1

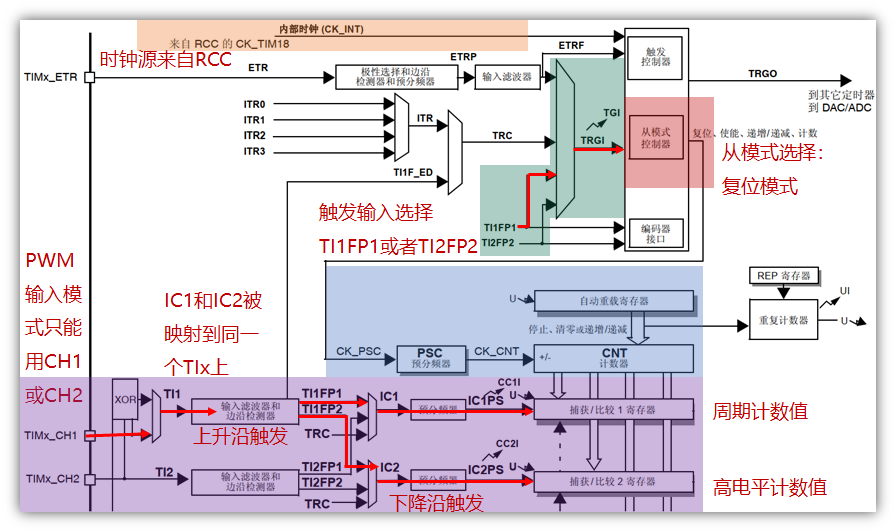

4.6 高级定时器PWM输入模式

4.6.1 PWM输入模式工作原理

4.6.2 PWM输入模式时序

4.6.3 高级定时器PWM输入模式配置步骤

评论区