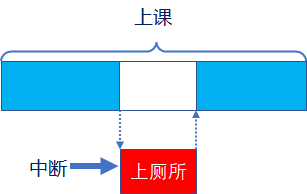

1. 中断的定义

简介:让CPU打断正常运行的程序,转而去处理紧急的事件(程序),就叫中断

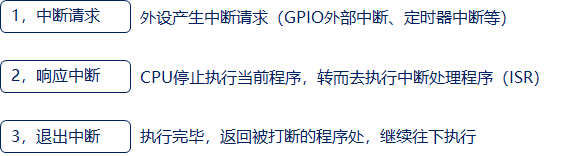

中断执行机制,可简单概括为三步:

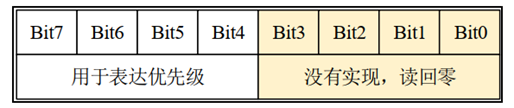

2. 中断优先级分组设置

- ARM Cortex-M 使用了 8 位宽的寄存器来配置中断的优先等级,这个寄存器就是中断优先级配置寄存器

- 但STM32,只用了中断优先级配置寄存器的高4位 [7 : 4],所以STM32提供了最大16级的中断优先等级

- STM32 的中断优先级可以分为抢占优先级和子优先级

- 抢占优先级: 抢占优先级高的中断可以打断正在执行但抢占优先级低的中断

- 子优先级: 当同时发生具有相同抢占优先级的两个中断时,子优先级数值小的优先执行,但不能互相打断

- 注意: 中断优先级数值越小越优先

一共有 5 种分配方式,对应着中断优先级分组的 5 个组

- 函数

HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4)即可完成设置,HAL_Init中会调用该函数

特点:

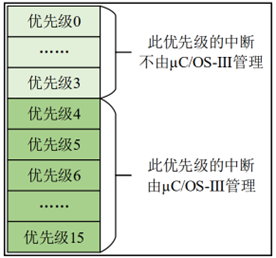

- UCOSIII的中断管理范围,通过宏CPU_CFG_KA_IPL_BOUNDA设置。如将该宏定义为4,即管理中断优先级范围:4 ~ 15

- 建议将所有优先级位指定为抢占优先级位,方便UCOSIII管理

- 中断优先级数值越小越优先,任务优先级同理

在中断服务函数中,如果调用到UCOSIII的API函数,那么该中断优先级必须在UCOSIII所管理的范围内

3. 中断相关寄存器

三个系统中断优先级配置寄存器,分别为 SHPR1、 SHPR2、 SHPR3

uC/OS-III配置PendSV和Systick中断优先级

- PendSV设置最低:保证系统任务切换不会阻塞系统其他中断的响应!

- SysTick设置所管理的最高:保证系统时钟节拍的精度!

- PendSV设置最低优先级,SysTick设置为UCOSIII所管理的最高优先级

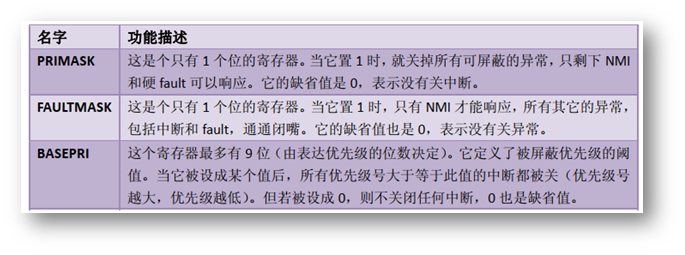

中断相关寄存器

- 三个中断屏蔽寄存器,分别为 PRIMASK、 FAULTMASK 和BASEPRI

- 在uC/OS-III中,中断屏蔽寄存器主要用到了BASEPRI 和 PRIMASK

- 其中中断管理就是利用BASEPRI这个寄存器,当需要关闭大部分中断时则使用PRIMASK这个寄存器

BASEPRI:屏蔽优先级低于某一个阈值的中断,当设置为0时,则不关闭任何中断

当BASEPRI设置为0x40时中断管理示意图:

进入临界区,以及退出临界区,就是操作BASEPRI寄存器

PRIMASK 寄存器有 32bit,但只有 bit0 有效,是可读可写的,将 PRIMASK 寄存器设置为 1 用于屏蔽除 NMI 和 HardFault 外的所有异常和中断,将 PRIMASK 寄存器清 0 用于使能中断。

评论区